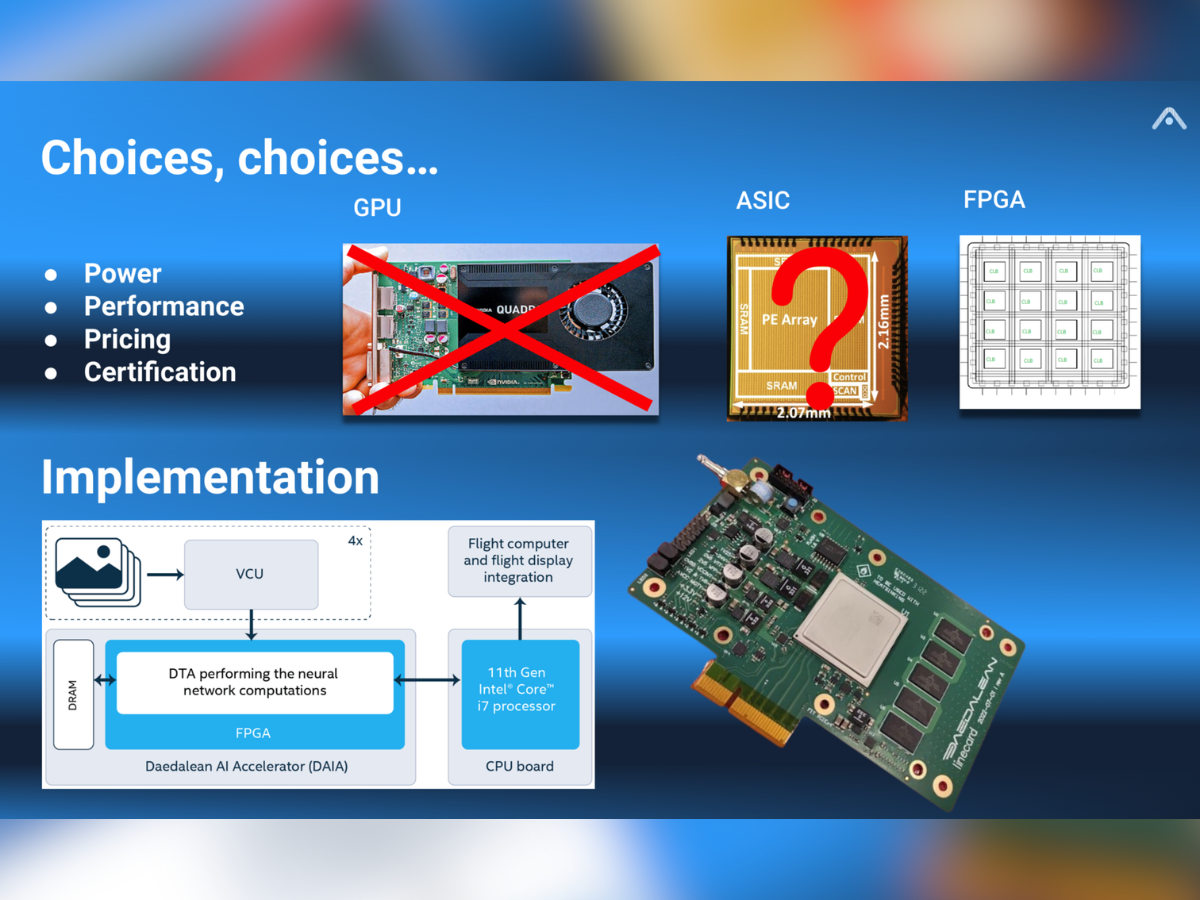

At Embedded World 2024, Daedalean’s Director of Engineering, Dr. Niels Haandbaek, presented a paper describing the architecture of the Daedalean Tensor Accelerator (DTA) and how it made possible computing performance never before seen on a platform satisfying performance, pricing, and certification requirements.

The paper, FPGA Design and Implementation of a High-Performance Avionics Certifiable CNN Accelerator, co-authored by Dr. Haanbaek, Johannes Frohnhofen, Christoph Glattfelder, Marc Gantenbein, Max Wipfli, Noam Gallmann, and Dr. Sota Sawaguchi, details experimental results of the research we first mentioned in a web post which outlined Daedalean’s exploration of GPU- to ASIC- and finally FPGA-based processing solutions.

This article was originally published by Daedalean.